This week on the IEEE Electronic Components and Packaging Technology Conference, Intel unveiled that it’s growing new chip packaging know-how that can permit for larger processors for AI.

With Moore’s Regulation slowing down, makers of superior GPUs and different information middle chips are having so as to add extra silicon space to their merchandise to maintain up with the relentless rise of AI’s computing wants. However the most measurement of a single silicon chip is fastened at round 800 sq. millimeters (with one exception), in order that they’ve needed to flip to advanced packaging technologies that combine a number of items of silicon in a approach that lets them act like a single chip.

Three of the improvements Intel unveiled at ECTC have been geared toward tackling limitations in simply how a lot silicon you possibly can squeeze right into a single package deal and the way massive that package deal may be. They embrace enhancements to the know-how Intel makes use of to hyperlink adjoining silicon dies collectively, a extra correct technique for bonding silicon to the package deal substrate, and system to broaden the scale of a crucial a part of the package deal that take away warmth. Collectively, the applied sciences allow the combination of greater than 10,000 sq. millimeters of silicon inside a package deal that may be larger than 21,000 mm2—a large space concerning the measurement of 4 and a half credit cards.

EMIB will get a 3D improve

One of many limitations on how a lot silicon can slot in a single package deal has to do with connecting a lot of silicon dies at their edges. Utilizing an natural polymer package deal substrate to interconnect the silicon dies is probably the most inexpensive choice, however a silicon substrate lets you make extra dense connections at these edges.

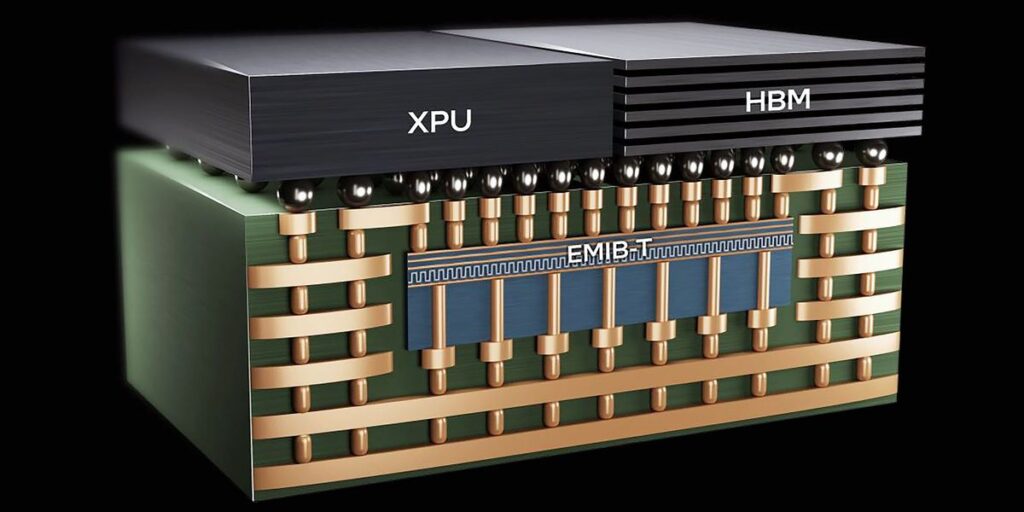

Intel’s resolution, launched greater than 5 years in the past, is to embed a small sliver of silicon within the natural package deal beneath the adjoining edges of the silicon dies. That sliver of silicon, known as EMIB, is etched with effective interconnects that enhance the density of connections past what the natural substrate can deal with.

At ECTC, Intel unveiled the most recent twist on the EMIB know-how, known as EMIB-T. Along with the standard effective horizontal interconnects, EMIB-T supplies comparatively thick vertical copper connections known as through-silicon vias, or TSVs. The TSVs permit energy from the circuit-board under to instantly connect with the chips above as a substitute of getting to route across the EMIB, decreasing energy misplaced by an extended journey. Moreover, EMIB-T accommodates a copper grid that acts as a floor airplane to cut back noise within the energy delivered as a result of course of cores and different circuits immediately ramping up their workloads.

“It sounds easy, however it is a know-how that brings quite a lot of functionality to us,” says Rahul Manepalli, vice chairman of substrate packaging know-how at Intel. With it and the opposite applied sciences Intel described, a buyer might join silicon equal to greater than 12 full measurement silicon dies—10,000 sq. millimeters of silicon—in a single package deal utilizing 38 or extra EMIB-T bridges.

Thermal management

One other know-how Intel reported at ECTC that helps enhance the scale of packages is low-thermal-gradient thermal compression bonding. It’s a variant of the know-how used at the moment to connect silicon dies to natural substrates. Micrometer-scale bumps of solder are positioned on the substrate the place they are going to connect with a silicon die. The die is then heated and pressed onto the microbumps, melting them and connecting the package deal’s interconnects to the silicon’s.

As a result of the silicon and the substrate broaden at completely different charges when heated, engineers should restrict the inter-bump distance, or pitch. Moreover, the growth distinction makes it troublesome to reliably make very giant substrates filled with numerous silicon dies, which is the course AI processors have to go.

The brand new Intel tech makes the thermal growth mismatch extra predictable and manageable, says Manepalli. The result’s that very-large substrates may be populated with dies. Alternatively, the identical know-how can be utilized to extend the density of connections to EMIB all the way down to about one each 25 micrometers.

A flatter warmth spreader

These larger silicon assemblages will generate much more warmth than at the moment’s programs. So it’s crucial that the warmth’s pathway out of the silicon isn’t obstructed. An built-in piece of steel known as a warmth spreader is vital to that, however making one sufficiently big for these giant packages is troublesome. The package deal substrate can warp and the steel warmth spreader itself won’t keep completely flat; so it won’t contact the tops of the new dies it’s purported to be sucking the warmth from. Intel’s resolution was to assemble the built-in warmth spreader in elements as a substitute of as one piece. This allowed it so as to add further stiffening elements amongst different issues to maintain the whole lot in flat and in place.

“Maintaining it flat at greater temperatures is a giant profit for reliability and yield,” says Manepalli.

Intel says the applied sciences are nonetheless within the in R&D stage and wouldn’t touch upon when these applied sciences would debut commercially. Nevertheless, they are going to doubtless should arrive within the subsequent few years for the Intel Foundry to compete with TSMC’s planned packaging expansion.

From Your Web site Articles

Associated Articles Across the Net